Press Release

Sumitomo Electric Launches High Quality SiC Epitaxial Wafer " EpiEra™"

October 12, 2017

Sumitomo Electric Industries, Ltd.

*This press release was originally published in Japanese on September 14, 2017.

Sumitomo Electric Industries, Ltd. has launched a high quality SiC epitaxial wafer, "EpiEra™", which attains a more than 99% defect free area in a wafer.

Power devices are semiconductor devices used in a wide range of applications such as power transmission, trains, automobiles, and electric appliances. They are increasingly required to offer higher efficiency at lower energy consumption.

SiC-based devices are expected to be a key component for energy-efficient solutions, and the demand is rapidly growing. However, to satisfy this demand and to compete with the yields and reliability of Si-based devices, material improvements are necessary.

Utilizing its multi-parameter and zone (MPZ™*1) control technology and 30-year experience in compound semiconductor development, Sumitomo Electric has succeeded in developing a high-quality SiC epitaxial wafer, "EpiEra™", and entered mass production stage.

EpiEra™ has achieved an industry-leading 99% defect-free area (DFA*2), eliminating surface defects*3 and Basal Plane Dislocations (BPD*4). This improves its quality stability and reliability.

Sumitomo Electric showcased this product at International Conference on Silicon Carbide and Related Materials (ICSCRM) 2017 held in Washington D.C., USA on September 17-22, 2017.

The Company continues to contribute to the SiC-based power electronics industry through the development of SiC devices with even higher efficiency and lower energy consumption.

-

SiC epitaxial wafers

-

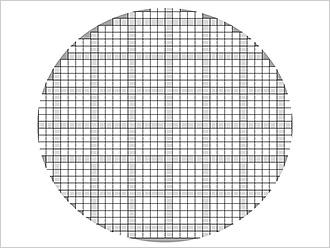

4-inch EpiEra™ BPD map

*1 Multi-parameter and zone controlled SiC growth technology (MPZ):

Sumitomo Electric's SiC growth technology that adjusts various parameters depending on the area and time zone utilizing simulation and monitoring techniques. Parameters include temperature, pressure, gas reactions, and others.

*2 Defect-free area (DFA):

An area with no surface defect or basal plane dislocation (BPD) on the wafer surface.

*3 Surface defect:

Morphological irregularity on the epitaxial layer surface. It impacts the device yield.

*4 Basal Plane Dislocations (BPD):

Dislocation generated on the basal plane in a SiC single crystal. It impacts the long-term device reliability.