# InP-DHBT Fabricated on High Heat Dissipation SiC Wafer Using Atomic Diffusion Bonding

Masataka WATANABE\*, Masaki YANAGISAWA, Katsumi UESAKA, Mitsuru EKAWA and Hajime SHOJI

The drastic increase in internet traffic has created the demand for ultra-high speed optical fiber communication systems that can transmit at a speed of over 400 Gbit/s. InP-based double heterojunction bipolar transistors (InP-DHBTs) with a high-speed transmission capability and high breakdown voltage are suitable for integrated circuits (ICs) that drive the semiconductor lasers or optical modulators in these fiber communication systems. In general, InP-DHBTs must be driven under a high current density for high baud rate operation. However, such severe operating conditions eventually accelerate the degradation of InP-DHBT characteristics because of self-heating, leading to shorter life of ICs. This paper introduces our trials to fabricate InP-DHBTs on a SiC wafer with high heat dissipation. Atomic diffusion bonding, which allows metal-metal bonding under room temperature and low pressure conditions, is used to fabricate the InP-DHBTs on a SiC wafer. The fabricated device reduces thermal resistance by more than 40% owing to the high heat dissipation of the SiC wafer.

Keywords: InP-based double heterojunction bipolar transistor (InP-DHBT), atomic diffusion bonding, thermal resistance, SiC wafer

## 1. Introduction

Video streaming, as on smartphones, and a variety of cloud computing services are increasingly becoming part of people's everyday lives. As a result, Internet traffic is ever increasing. In line with this trend, development of ultrafast fiber-optic communication systems operating at over 400 Gbit/s is under way. In optical communication systems, driver ICs that drive semiconductor lasers or optical modulators require transistors that are fast and have a high breakdown voltage. To use them with driver ICs that support up to 100 Gbit/s of baud rates, Sumitomo Electric Industries, Ltd. developed an InP-based double heterojunction bipolar transistor (InP-DHBTs),\*1 the characteristics of which are  $f_T$  = 180 GHz,  $f_{max}$  = 200 GHz,\*2 and BV\_{ceo} >5 V.\*<sup>3,(1),(2)</sup> To meet demand for even higher baud rates, it is necessary to operate InP-DHBTs at a high current density. However, these harsh operating conditions pose the problem of self-heating in InP-DHBTs, accelerating characteristic degradation and reducing their usable life. With respect to this, in recent years, several reports have been published on the use of a wafer bonding technique to fabricate a transistor on a high-heat dissipation SiC wafer.<sup>(3),(4)</sup> While the use of resin is a convenient way of achieving wafer bonding, metal-metal or direct bonding is more suitable in terms of heat dissipation. Metal-metal and direct bonding processes are generally performed under high-temperature, high-pressure conditions. However, from the perspective of avoiding strain resulting from disparity in the coefficient of linear thermal expansion of wafers and avoiding damage caused by high-pressure conditions, bonding should desirably be performed under room-temperature and low-pressure conditions. In the present study, we succeeded in fabricating an InP-DHBT on a SiC wafer, using atomic diffusion bonding\*4,(5),(6) that enables metal-metal bonding at room temperature and under low pressure. This paper reports on the fabrication process and the typical characteristics of the newly fabricated InP-DHBT.

## 2. Fabrication Process

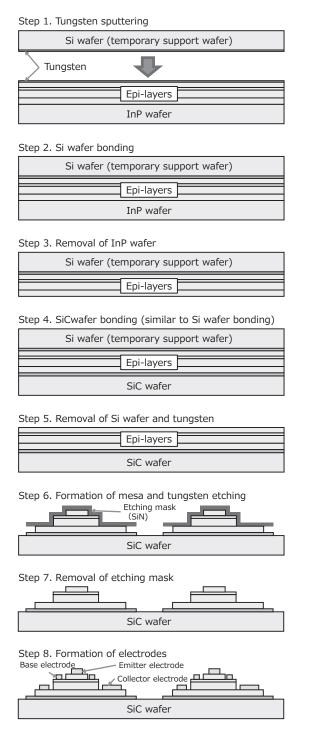

For the purpose of wafer bonding, epitaxial growth is usually achieved in the reverse sequence because otherwise epitaxial growth layers (epi-layers) would be oriented inversely with respect to the mating wafer. However, because the quality of epi-layers is affected by the growth sequence, it is difficult to accurately verify the characteristics of semiconductor devices that incorporate epi-layers grown in the reverse sequence. We have made it possible to use epi-layers grown in the ordinary sequence by transferring them twice through wafer bonding. Figure 1 shows the process of InP-DHBT fabrication on a SiC wafer. In this process, epitaxial growth layers formed on an InP wafer undergo wafer bonding twice so as to be transferred onto a SiC wafer, followed by the processing of the transferred epi-layers into an InP-DHBT.

First, to prepare for atomic diffusion bonding, tungsten is sputtered onto the surfaces of epi-layers and a Si wafer, which is a temporary support wafer, by 5 nm each inside the chamber of a bonding system (Step 1). This is followed by atomic diffusion bonding with the condition unchanged between the epi-layers and the Si wafer in the same chamber. Bonding is carried out at a room temperature and below 10 kPa (Step 2).

Subsequently, the InP wafer is removed by etching with dilute hydrochloric acid (Step 3). Atomic diffusion bonding is performed between the underside of the epilayer exposed in Step 3 and a SiC wafer under the same conditions as in Steps 1 and 2 (Step 4). The Si wafer is removed by etching with a potassium hydroxide solution to expose tungsten. The exposed tungsten is then removed by dry etching using CF<sub>4</sub> gas (Step 5) to complete the epilayer transfer process. Next, using a SiN film as a mask, the epi-layers are wet-etched to sequentially form mesas for an InP-DHBT. This process continues until tungsten is exposed. The exposed tungsten is removed by dry etching using CF<sub>4</sub> gas (Step 6). Next, the SiN mask is removed with a dilute hydrofluoric acid (Step 7). Emitter, base, and collector electrodes are formed by vacuum evaporation (Step 8). This is followed by ordinary patterning to complete the fabrication of an InP-DHBT on a SiC wafer.

Fig. 1. Fabrication process

## 3. Results from Prototypes

## **3-1** Appearance

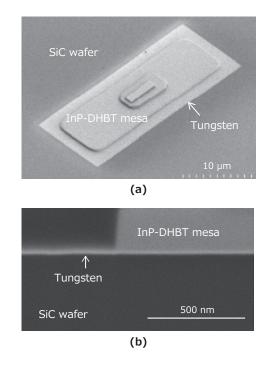

Figure 2 (a) shows a scanning electron microscopy (SEM) image of an InP-DHBT mesa formed on a SiC wafer (Step 7 in Fig. 1). Figure 2 (b) shows an SEM image of a cross-section of the bonding interface. A very small 7  $\mu$ m × 20  $\mu$ m mesa of InP/InGaAs is formed on the SiC wafer with a thin tungsten film in between. The tungsten film, the bonding interface, is of good quality, containing no void or unbonded areas, which results in reduced heat dissipation. This section presents the results of a characteristic comparison between the InP-DHBT formed on a SiC wafer and the conventional InP-DHBT on an InP wafer.

Fig. 2. SEM images (a) InP-DHBT mesa formed on SiC wafer (b) Cross section of bonding interface

## **3-2** Thermal resistance

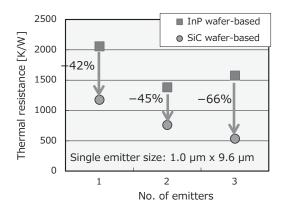

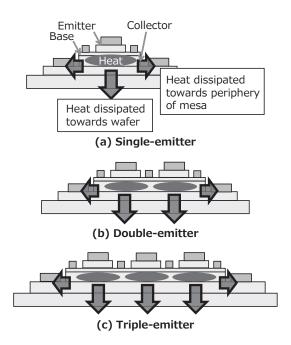

To make a heat dissipation evaluation, the thermal resistance\*5 of InP-DHBTs was measured. This thermal resistance evaluation was conducted for a multi-emitter structure as well as for a normal single-emitter structure. The multi-emitter structure comprised a row of multiple emitters laid in parallel to output a relatively large current. A large output current leads to an increasing amount of self-heating. Hence, heat dissipation becomes of greater significance for the multi-emitter structure. Figure 3 shows the thermal resistance measurement results. The InP-DHBT formed on a SiC wafer exhibited substantial reduction in thermal resistance, outperforming the conventional InP-DHBT formed on an InP wafer by more than 40%. The benefits of reduced thermal resistance are noticeable specifically with the multi-emitter structure. Heat dissipation paths from the heat generating section of the InP-DHBT possibly fall into two groups: towards the wafer and towards the peripheries of mesas, as shown in Fig. 4. It is inferred that the effect of improved heat dissipation from the wafer is more noticeable with an increasing number of emitters because with each additional emitter the proportion of heat dissipated through the wafer increases. Consequently, it is highly probable that this technique is specifically effective for a multi-emitter structure that handles large currents.

Fig. 3. Thermal resistance measurement results

Fig. 4. Rendered image of heat dissipation paths

#### 3-3 DC characteristics

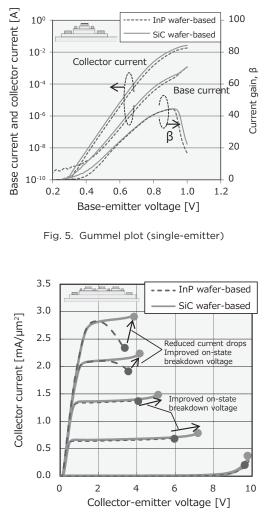

Figure 5 shows a Gummel plot\*<sup>6</sup> of InP-DHBTs. These InP-DHBTs have a single-emitter structure, with the emitter size being 1.0  $\mu$ m × 9.6  $\mu$ m. The current gain  $\beta$  of the InP-DHBT fabricated on a SiC wafer is at a similar level to the conventional InP-DHBT built on an InP wafer, indicating that bonding caused no damage or other detrimental effects. Figure 6 shows the current-voltage charac-

teristics (common emitter) of a triple-emitter structure, in which each emitter was 1.0  $\mu$ m × 9.6  $\mu$ m in size. To make a breakdown voltage evaluation, the collector-emitter voltage was swept until the breakdown of InP-DHBTs (dots represent breakdown). The InP-DHBT fabricated on a SiC wafer exhibited 0.5 to 1.0 V improvements in on-state breakdown voltage.\*<sup>7</sup> Moreover, current drops observed during high-power operation reduced. These improvements can be attributed to enhanced heat dissipation.

Fig. 6. Common emitter current-voltage characteristics (triple-emitter)

#### 3-4 High-frequency characteristics

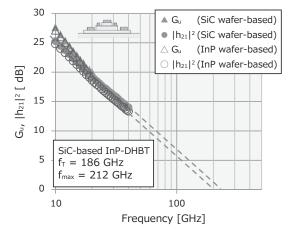

Figure 7 shows the frequency dependence of the current gain  $(|h_{21}|^2)$  and the maximum unilateral power gain (G<sub>u</sub>) calculated based on S-parameters measured within a frequency range between 10 and 40 GHz using a high-frequency measurement system (Keysight 8510C). The object of the measurement was an HBT that has a single-emitter structure and is 1.0  $\mu$ m × 9.6  $\mu$ m in size. The parasitic capacitance of the pad was removed through calibration. The InP-DHBTs formed on a SiC wafer exhibited fr = 186 GHz and f<sub>max</sub> = 212 GHz under the following voltage

and current conditions:  $V_{ce}$  (collector-emitter voltage) = 2.0 V and I<sub>c</sub> (collector current) = 18 mA. This performance is on par with the high-frequency characteristics of conventional InP-DHBTs fabricated on an InP wafer, which are indicated with white circles and triangles plotted on the same graph. Consequently, the bonding is unlikely to have caused any degradation.

Fig. 7. High-frequency characteristics (single-emitter)

### 4. Conclusion

An InP-DHBT was fabricated on a high-heat dissipation SiC wafer by means of atomic diffusion bonding in order to improve device characteristics by enhanced heat dissipation. Device fabrication on a high-heat dissipation SiC wafer reduced thermal resistance of an InP-DHBT by more than 40%, resulting in an improved on-state breakdown voltage and suppression of a current drop during highcurrent operation. Moreover, the DC and high-frequency characteristics of the newly developed device were normal, demonstrating that the use of the wafer bonding process had no detrimental effect on the device.

The results of this study appear to open the way to faster InP-DHBTs by driving them under high current density. Our future tasks include assessing the reliability of the newly developed InP-DHBT and ascertaining the effect of this technique on the service life of the device.

#### 5. Acknowledgements

This study was conducted as a joint research project with Professor Takehito Shimatsu of the Frontier Research Institute for Interdisciplinary Sciences, Tohoku University. We would like to express our grateful thanks to Professor Shimatsu.

#### **Technical Terms**

- \*1 Double heterojunction bipolar transistor (DHBT): A DHBT is a fast transistor with a high breakdown voltage.

- \*2 fr, fmax:

$f_{T}$  (cut-off frequency): the frequency at which current gain reaches 1.

f<sub>max</sub> (maximum oscillation frequency): the frequency at which power gain reaches 1. Both are indexes for measuring the operation speed

of a transistor.

- \*3 BV<sub>cco</sub>: Collector-emitter breakdown voltage with the base being open

- \*4 Atomic diffusion bonding: A bonding technique that uses atomic diffusion on thin metallic films or grain boundaries; Atomic diffusion bonding can be achieved at room temperature and under low-pressure conditions.

- \*5 Thermal resistance: An index for device heat dissipation; the lower the thermal resistance, the higher the heat dissipation.

- \*6 Gummel plot: A graph that plots the dependence of the base current and the collector current on the baseemitter voltage observed at a constant base-collector voltage; The ratio of the collector current to the base current is the current gain.

- \*7 On-state breakdown voltage: Breakdown voltage between collector and emitter in an energized (on) state.

#### References

- M. Yanagisawa, M. Watanabe, T. Kawasaki, H. Kobayashi, K. Kotani, R. Yamabi, Y. Tosaka, and D. Fukushi, "Highly-reliable and reproducible InGaAs/InP double heterojunction bipolar transistor utilizing all-wet etching process for triple mesa formation," Bipolar/ BiCMOS Circuits and Technology Meeting, pp. 97–100 (2013)

- (2) T. Tatsumi, "Development of Electro-Absorption Modulator Driver ICs for 25G/40G Transmission," SEI TECHNICAL REVIEW No. 74 (April 2012)

- (3) D. W. Scott, C. Monier, S. Wang, V. Radisic, P. Nguyen, A. Cavus, W. R. Deal, and A. Gutierrez-Aitken, "InP HBT transferred to higher thermal conductivity substrate," IEEE Electron Device Lett., vol. 33, no. 4, pp. 507–509 (Apr. 2012)

- (4) A. Thiam, Y. Roelens, C. Coinon, V. Avramovic, B. Grandchamp, D. Ducatteau, X. Wallart, C. Maneux, and M. Zaknoune, "InP HBT thermal management by transferring to high thermal conductivity silicon substrate," IEEE Electron Device Lett., vol. 35, no. 10, pp. 1010–1012 (Oct. 2014)

- (5) T. Shimatsu and M. Uomoto, "Atomic diffusion bonding of wafers with thin nanocrystalline metal films," J. Vac. Sci. Technol. B, vol. 28, pp. 706–714 (2010)

- (6) T. Shimatsu, M. Uomoto, and H. Kon, "Room temperature bonding using thin metal films (bonding energy and technical potential)," ECS Transactions, vol. 64, no. 5, pp. 317–328 (2014)

**Contributors** The lead author is indicated by an asterisk (\*).

# **M. WATANABE\***

• Assistant General Manager, Transmission Devices Laboratory

# M. YANAGISAWA

• Ph.D

Assistant General Manager, Transmission Devices Laboratory

# **K. UESAKA**

Project Leader, Transmission Devices Laboratory

# M. EKAWA

Ph.D Group Manager, Transmission Devices Laboratory

# H. SHOJI

• Ph.D Department Manager, Transmission Devices Laboratory