# Development of Via Connection Technology with Conductive Paste

Yoshio OKA\*, Takashi KASUGA, Hiroshi TOMIOKA, Sumito UEHARA, Jin Joo PARK, Naota UENISHI and Yasuhiro OKUDA

Flexible printed circuit (FPC) boards need to have fine pitch patterns for lighter, thinner, and smaller electronic equipment, and connection technology for metal layers (other than copper) is required for FPC diversification. Conductive paste via connection technology offers advantages for manufacturing fine pitch FPC boards and can be applied to non-copper metal layers. The authors have developed highly reliable via connecting technology using conductive paste containing silver nano particles.

Keywords: FPC, conductive paste, nano particle, via connecting

## 1. Introduction

Flexible printed circuit (FPC) boards need to have fine pitch patterns for lighter, thinner, and smaller electronic equipment.

Since FPC development started in the research section in 1969, Sumitomo Electric Industries, Ltd. has developed products which meet the needs of the electronics industry through the development of specific technologies based on its creativity and copper wire production technology<sup>(1)</sup>.

In recent years, with the progress of digitization, compact and lightweight electronic apparatus with advanced features has been developed, and accordingly, highly functional products using fine pitch flexible printed circuit (FPC) boards are needed.

To cope with this need, we have developed a high conductive paste which uses our original nano electric conductive particles and high reliability connection technology for metal layers with a small diameter via and non-conductive layers made from metal other than copper.

## 2. Paste Connection Technology

## 2-1 Connection technology using conductive paste

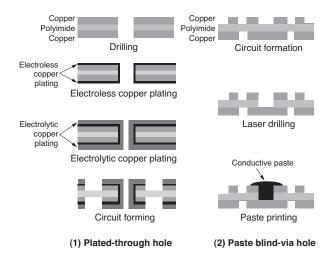

In a double-sided FPC, a copper layer covers both sides of the core polyimide (PI) film, and conduction is normally achieved through the copper plating of holes that pass through the core layer between the copper layers. This method is called plated-through hole (PTH). It consists of four processes: NC drilling, non-electrolytic plating, electrolytic plating, and circuit formation by etch process (**Fig. 1(1)**). The method has disadvantages in fine pitch circuit formation because the copper layer becomes thick.

On the other hand, paste connection technology consists of three processes: circuit formation by etch process, via formation by laser or other devices, and printing using conductive paste with conductive filler and resin (**Fig. 1(2**)). Therefore this method has advantages in fine pitch circuit

Fig. 1. Conceptual diagram of interlayer connecting process

patterning, because the copper thickness is the same as the original substrate.

## 2-2 Conductive paste

We have established a metal nano-particle manufacturing process using our innovative liquid phase process based on the plating technology. Eliminating the use of a vacuum system, this process manufactures uniformly-sized particles at a low cost<sup>(2)</sup>.

Nickel nano-particles and silver nano-particles have already been used in anisotropic conductive film (ACF) and conductive ink for printed wiring material<sup>(3), (4)</sup>.

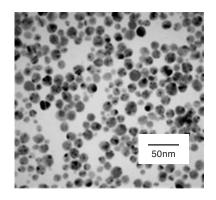

Paste via connection technology using conductive paste with nano silver particles (**Photo 1**) and micron-sized conductive particles has high reliability performance as described later in this paper.

The mixing ratio of resin, additives and the conductive particles of the conductive paste has been optimized. At a stage of material design, improvement of ion migration and compliance with the RoHS directive and other environmental regulations were taken into consideration.

Photo 1. TEM observation of silver nanoparticles

## 2-3 Via-filling using conductive paste

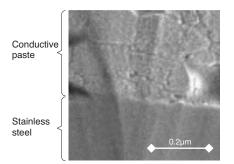

**Photo 2 and 3** show a cross section of blind via holes (hole diameters are  $60 \ \mu m$  and  $40 \ \mu m$ ) by screen printing using conductive paste, and the vias are filled up with the conductive paste. **Photo 4** shows the interface of the conductive paste and stainless steel. There is no intervention layer and it is connected well.

**Photo 2.** Cross section of ø60µm blind via using the conductive paste

**Photo 3.** Cross section of ø40µm blind via using the conductive paste

Photo 4. Interface of conductive paste and stainless steel

## 2-4 Reliability

(1) Evaluation test sample

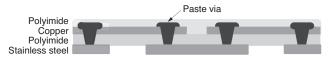

Evaluation of reliability test was carried out using an evaluation test sample which has a cross-sectional structure as shown in **Fig. 2**.

This sample has blind via holes (hole diameter is 60  $\mu m$ ), and circuits form a daisy chain pattern, in which the

Fig. 2. Institute of evaluation test sample (daisy chain pattern) via /land diameter =ø60μm/ø120μm

first conductive layer is made of copper, and second one is made of stainless steel. We measured the total resistance of the entire vias and circuits.

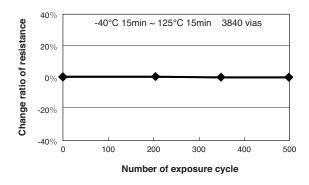

(2) Heat shock test

This sample was tested by a thermal shock testing machine which was set at -40 degrees Celsius as the lowest temperature and 125 degrees Celsius as the highest temperature, to evaluate the change in resistance. The result is shown in **Fig. 3**. The resistance remained unchanged after being exposed to a heat shock.

Fig. 3. Connection reliability in heat shock test

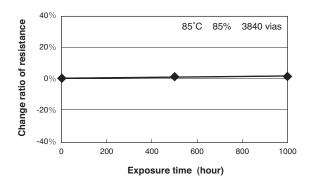

## (3) High temperature and humidity test

**Figure 4** shows the test results at a high temperature (85 degrees Celsius) and high humidity (85%). The resistance remained unchanged after being exposed to the high temperature and high humidity.

Fig. 4. Connection reliability in high temperature and humidity test

The Highly Accelerated temperature and humidity Stress Test (HAST)<sup>\*3</sup> (120 degrees Celsius, 85%, 96 h) was also carried out for the same sample. The resistance changed by 1% during HAST.

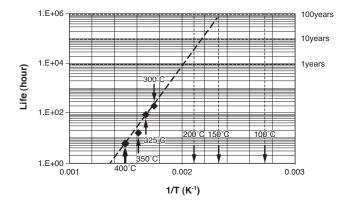

(4) Heat resistance evaluation

In order to evaluate their heat resistance in the atmosphere, the test samples were subject to high temperatures (300, 325, 350 and 400 degrees Celsius). When the resistance increased to 20% or higher, the product was regarded as having reached the end of service life. **Figure 5** shows an Arrhenius plot of the heat test result. At 150 degrees Celsius, at least 10 years or more of life expectancy can be expected, and this connection technology shows high heat resistance reliability.

Fig. 5. Test result of heat resistance test

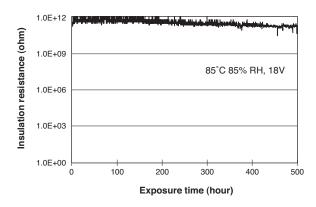

(5) Ion migration evaluation

A DC voltage of 18 V was applied to the neighboring circuits (15  $\mu$ m space) including conductive paste vias (diameters are 60  $\mu$ m and 120  $\mu$ m). Insulation resistance was also monitored. As shown in **Fig. 6**, its insulation resistance remained over 10G $\Omega$  for 500 hours. This result means that our via connection technology has superior insulation reliability.

Fig. 6. Insulation reliability at high temperature and humidity test

(6) Flex resistance

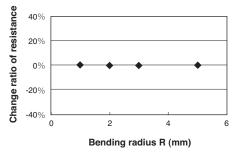

Even in conventional plated-through holes, an interlayer connection portion is not used for the bending portion. In order to evaluate the tolerance to mechanical strains, the following experiments were conducted. **Figure 7** shows the diagrammatic illustration of this bending test. We used bending jigs which are made of brass and have curvature radius of 1, 2, 3 and 5 mm. The sample was slid along the jig (see **Fig. 7**). The procedure of the experiment is as follows: (1) the stainless steel side of the sample is arranged inside and slid along the jig and (2) the stainless steel side of the sample is arranged outside and slid along the jig. The operation (1) and (2) were carried out 6 times (24 times of bending in total).

**Figure 8** shows the result of this bending test. This conductive paste via has a high reliability for mechanical strain as there is little resistance change after the test.

As shown in the above mentioned test results, our connection technology using the conductive paste shows high reliability with good resistance to high temperature, humidity, ion migration, and bending.

Fig. 7. Diagrammatic illustration of the bending test

Fig. 8. Result of the bending test

## 3. Conclusion

We have developed a conductivity paste which uses the original nano electric conduction particles and our compound material technology. By using this paste, small diameter via holes can be filled well and via holes with non-copper metal layers can be connected. This interlayer connection shows high reliability in the tests of heat shock, heat resistance, constant temperature and humidity, ion migration, and bending.

# **Technical Terms**

- \*1 Restriction of Hazardous Substances (RoHS): The directive on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

- \*2 Daisy Chain Pattern: A bumper-to-bumper wiring method which connects multiple sites.

- \*3 Highly Accelerated temperature and humidity Stress Test (HAST): A steam test conducted in a non-saturating autoclave for testing reliability of electronic components under temperature and humidity stress.

#### References

- (1) Masayuki Kanehiro, Shuji Kashiwagi, Kouki Nakama, Juichiro Nishikawa, Hideo Aramaki, "Development of Sumitomo Electric's Flexible Printed Circuit business," SEI Technical Review, P.4-13, No.66 (2008)

- (2) Masatoshi Majima, Keiji Koyama, Yoshie Tani, Hideaki Toshioka, Misako Osoegawa, Hideaki Kashihara, Shinji Inazawa, "Development of Conductive Material Using Metal Nano Particles," SEI Technical Review, P.25-27, No.54 (2008)

- (3) Hideaki Toshioka, Kyouichirou Nakatsugi, Masamichi Yamamoto, Katsuhiro Sato, Naoki Shimbara, Yasuhiro Okuda, "Development of Anisotropic Conductive Film for Narrow Pitch Circuits," SEI Technical Review, p.40-44, No.73 (2011)

- (4) Issei Okada, Kouhei Shimoda, Takeshi Miyazaki, "Development of Fine Circuit Pattern Formation Process Using Nano-Metal Ink," SEI Technical Review, p.54-57, No.62 (2006)

# Contributors (The lead author is indicated by an asterisk (\*).)

# Y. OKA\*

Group Manager, Electronics & Material R&D Laboratories

Engaged in the research and development of FPCs.

# T. KASUGA

• Assistant Manager, Electronics & Material R&D Laboratories

# H. TOMIOKA

• Sumitomo Electric Printed Circuits, Inc.

# S. UEHARA

• Assistant Manager, Sumitomo Electric Printed Circuits, Inc.

# J. J. PARK

• Manager, Sumitomo Electric Printed Circuits, Inc.

# N. UENISHI

• General Manager, Development Department, Sumitomo Electric Printed Circuits, Inc.

# Y. OKUDA

- Ph.D

- Department Manager, Electronics & Material R&D Laboratories